# Module Management Controller for MicroTCA-based Controller Board

Piotr Perek, Aleksander Mielczarek, Paweł Prędki, Dariusz Makowski, *Member, IEEE*, and Andrzej Napieralski, *Senior Member, IEEE*

Abstract—As a result of a growing interest in the xTCA systems by research centers conducting High Energy Physics (HEP) experiments, the PICMG xTCA for Physics Coordinating Committee is developing a new, attractive standards. They are specifically dedicated to control and data acquisition systems of HEP applications. These new specifications define a number of extensions to the Advanced Telecommunications Computing Architecture (ATCA) and Micro Telecommunications Computing Architecture ( $\mu$ TCA) standards.

The MicroTCA for Physics specification, named MTCA.4, defines some new solutions in order to simplify an application of  $\mu$ TCA specification in HEP facilities. The most important of them is  $\mu$ RTM module which can be connected to the Advanced Mezzanine Card (AMC) and provides more usable area and additional I/O connectors at the rear of the shelf. The MTCA.4 also introduces additional channels dedicated for timing and synchronization signals that are available on backplane.

Due to the fact that xTCA for Physics is a new specification which has not been officially published, both the AMC and  $\mu$ RTM modules and the software for the MMC with possibility of  $\mu$ RTM handling are not yet available. For this reason the preparation of firmware for the Module Management Controller (MMC) for AMC modules compatible with MicroTCA for Physics specification is required.

This paper presents a structure of the MMC for the  $\mu$ TC (MicroTCA-based Controller) board. It also describes the microcontroller software which fulfills the role of the MMC.

Index Terms—Micro Telecommunications Computing Architecture, MicroTCA, Module Management Controller, xTCA for Physics

# I. INTRODUCTION

THE Micro Telecommunications Computing Architecture  $\blacksquare$  ( $\mu$ TCA, MicroTCA) standard [1] is a series of PICMG specifications developed on the base of Advanced Telecommunications Computing Architecture (ATCA) [2] and Advanced Mezzanine Card (AMC) [3] specifications. This standard is specifically dedicated for telecommunications and enterprise computer network equipment. It incorporates actual trends in the field of high speed-interfaces and ensures high level of reliability and availability. The  $\mu$ TCA is also distinguished by modular construction which makes the system easy scalable and gives the possibility of flexible configuration of system functionality. It is worth emphasizing that systems based on  $\mu$ TCA specification also provide the Hot Swap mechanism. It allows to exchange the modules during normal system operation, without the need of turning off the power supply. The Hot Swap mechanism makes the system service and maintenance much easier and is one of the reasons of high level of availability.

All of the mentioned features mean that the  $\mu$ TCAbased systems are used not only in telecommunications and computing applications, but also in High Energy Physics (HEP) facilities.  $\mu$ TCA finds application in control and data acquisition systems in various machines such as colliders [4] and accelerators [5]–[7]. The growing interest of HEP community in  $\mu$ TCA as well as ATCA standards decided an PICMG xTCA for Physics Coordinating Committee establishment. This committee is working on adjustment of xTCA standards to the needs of HEP. It is developing new, attractive specifications - xTCA for Physics - that define extensions for xTCA standards and facilitate their use in data acquisition and control systems. The most important of these extensions are rear I/O and additional channels on the backplane dedicated for distribution of clock, trigger and interlock signals [8].

# II. MANAGEMENT LAYER IN MICROTCA FOR PHYSICS SPECIFICATION

The MicroTCA for Physics specification, named MTCA.4, concerns application of MicroTCA systems in HEP facilities. It defines the Advanced Mezzanine Card (AMC) and Micro Rear Transition Module ( $\mu$ RTM) as well as an appropriate  $\mu$ TCA shelf in which they can be used. The outline of the AMC for Physics Module described in MTCA.4 specification is virtually the same as the outline of Double Module defined in the AMC.0 specification [3]. Small differences result from adding additional connectors which make the  $\mu$ RTM connection possible.

An essential problem in case of complex control systems of HEP machines is a large number of signals which must be supplied to the system from the outside [9], [10]. That is why the  $\mu$ TCA for Physics specification defines a new module, called  $\mu$ RTM. The  $\mu$ RTM boards are placed in the rear of the subrack and can be connected to the AMC Front Boards. Its most important feature is providing a large number of inputs or outputs on the rear. The outline of the  $\mu$ RTM is similar to that of the AMC module. This means that the total usable area of the compound boards is twice as big as in case of typical  $\mu$ TCA systems. Moreover, the equal size of the AMC and the  $\mu RTM$  modules enables flexible combinations to design a modular system. The AMC board may be designed as a more complex, base module while the  $\mu$ RTM acts as the adapter. The usage of the  $\mu$ RTM module allows to separate digital and analog parts of the system.

The management layer in the  $\mu TCA$  for Physics specification is very similar to that specified in basic  $\mu TCA$

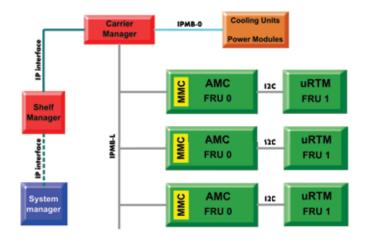

Fig. 1. Management layer of an exemplary  $\mu$ TCA for Physics shelf

standard [1], [11]. The structure of the management layer of an example system is presented in Figure 1. As in case of all xTCA systems, components of the management layer communicate with each other in accordance with principles of the IPMI standard [12]. The main management component in each system is the Shelf Manager which acts as the aggregation point and it can manage up to sixteen  $\mu$ TCA Carriers that comprise a  $\mu$ TCA Shelf. Each  $\mu$ TCA Carrier is controlled and managed by the Carrier Manager. It is responsible for directing module activation and deactivation processes, power and backplane interconnects management and also continuous monitoring of the modules. The Carrier Manager also represents all the modules in a  $\mu$ TCA Carrier.

The Carrier Manager has to communicate with local controllers of the AMC modules which are called Module Management Controllers (MMCs). The tasks of the MMCs are communication with the Carrier Manager for module activation and deactivation, power supply control and monitoring of operating parameters such as temperature, voltage and current. The MMC also participates in setting up connections for high-speed interfaces. A novelty introduced in MTCA.4 specification is application of dedicated connections for timing and synchronization signals. Because these connections are incompatible with typical E-Keying mechanisms, the MTCA.4 defines a special record which describes these connections.

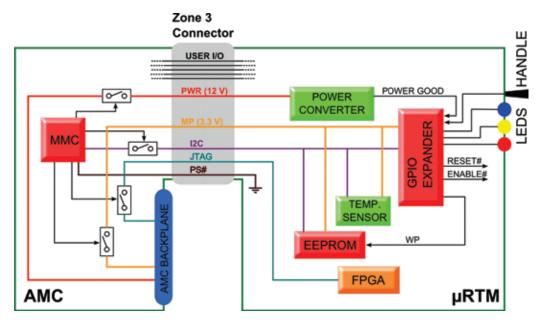

The situation is different in case of the  $\mu$ RTM. It does not require implementation of an intelligent management controller like the MMC because it is not connected directly to the Carrier Manager. The  $\mu$ RTM board is fully supervised by the MMC present on an AMC Front Board. Devices responsible for management of the AMC and  $\mu$ RTM modules as well as connections between them are presented in Figure 2. First of all, the AMC module is responsible for providing power supply to the  $\mu$ RTM module. The MMC controls and monitors both Management (3.3 V) and Payload Power (12 V). Moreover, the AMC Front Board has to ensure I²C bus for connection to devices on the  $\mu$ RTM.

The MMC of the AMC module is responsible for representing the  $\mu$ RTM in communication with the Carrier Manager. The  $\mu$ RTM is represented as an additional Field

Replaceable Unit (FRU) implemented by the MMC. This is one of the innovations introduced in the MTCA.4 specification. The MMC of the AMC module compliant with basic  $\mu$ TCA specification could implement only one FRU device and, consequently, it could not manage any other replaceable modules.

However, the  $\mu$ RTM has to make information about its sensors and high-speed interfaces available. All this information is stored in an EEPROM memory accessible by the AMC module over a dedicated I<sup>2</sup>C bus. The EEPROM contains a basic data structure, named the Platform Management FRU Information, defined in the IPMI standard. The data stored in this structure provides information about the  $\mu$ RTM. It is divided into various records and they can provide basic information about the  $\mu$ RTM as a whole (e.g. product number, product name, manufacturer name etc.), as well as information about the links provided by the  $\mu$ RTM. What is worth emphasizing, the MTCA.4 specification defines a new type of record, called the Interface Compatibility record which helps to determine if the  $\mu$ RTM is compatible with a given AMC board. Moreover, this specification defines hardware keying mechanism. The  $\mu RTM$  shall be equipped with mechanical male key of specified shape, while the AMC board shall implement appropriate receptacle. Orientation of the key on  $\mu$ RTM and receptacle on AMC board depends on the voltage level of provided signals. If voltage levels of signals provided by AMC and  $\mu$ RTM are different, connection of AMC board and  $\mu$ RTM is impossible. Therefore, both mentioned solutions, Interface Compatibility record and keying mechanism are aimed to protection from potential damages which can occur when an incompatible  $\mu$ RTM is connected to an AMC module.

Furthermore, the  $\mu$ RTM shall ensure at least one temperature sensor accessible by MMC of the AMC module, as well as a GPIO expander with I<sup>2</sup>C interface connected to the same bus as the EEPROM. This port expander gives the possibility to basic control of signals on the  $\mu$ RTM.

Summarizing, the MMC of the AMC Front Board has to ensure all basic functionalities imposed by AMC.0 and MicroTCA.0 specification. They include communication with the Carrier Manager, handling of commands compatible with the IPMI specification, module activation and deactivation, power management, sensor monitoring, E-keying mechanism as well as providing information about the module, sensors and provided connections. Furthermore, the MMC compatible with MTCA.4 is obliged to implement the following additional features:

- management of power supply for the  $\mu$ RTM module,

- representation of the  $\mu$ RTM in communication with the Carrier Manager,

- reading of information from EEPROM memory and control of devices placed on the  $\mu$ RTM module,

- verification of compatibility of the  $\mu$ RTM and AMC module.

Due to the fact that xTCA for Physics is a new specification which has not been officially published, both the AMC and  $\mu$ RTM modules and the software for the MMC with possibility of  $\mu$ RTM handling are not yet available on the market. This

Fig. 2. AMC/ $\mu$ RTM management

meant that the preparation of firmware for the MMC for AMC modules compatible with MTCA.4 specification was necessary.

#### III. MODULE MANAGEMENT CONTROLLER FOR $\mu TC$

The Module Management Controller described in this paper is a part of the  $\mu$ TCA-based Controller board. Description of this board is beyond the scope of this paper and further information about it can be found in [13].

#### A. Hardware Structure of MMC

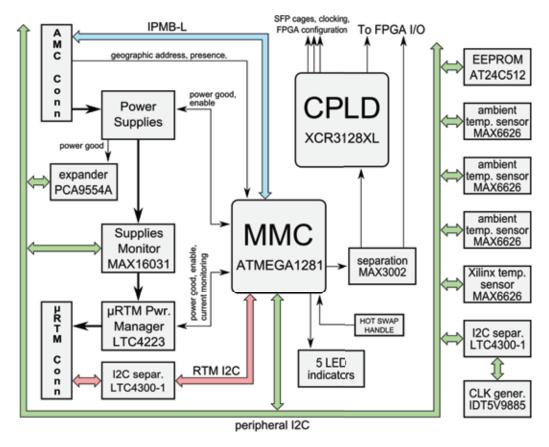

The structure of devices which consist of Module Management Controller is presented in Figure 3. The most important components are ATMEGA1281 microcontroller, which controls operation of another devices, and CPLD circuit, which acts as I/O expander. The microcontroller is directly connected to the IPMB-L bus and communicates with the supervising system. Along with the developed firmware its 8-bit core, clocked at 8 MHz generated by an external oscillator, implements all the required MMC controller features. The microcontroller provides information on the module condition and offers the means for controlling the power supply system and managing operational mode of the data processing payload. Using it's dedicated I/O lines and an I<sup>2</sup>C expander, it monitors supply voltages for onboard devices, measures the Payload Power line voltage and estimates the  $\mu$ RTM current consumption. All the DC/DC converters, and consequently the dependent LDO voltage regulators, are also under its control. The dedicated power supplies monitoring circuit additionally measures the overall module current consumption and provides the measurements of the eight most critical voltages. For compliance with  $\mu$ TCA for Physics specification both the  $\mu$ RTM voltages are also keyed on-board, enabling the hot-plug mechanism also for this module. Using the peripheral I<sup>2</sup>C bus, the controller collects temperature readouts from four points on the board and also from the FPGA die – using a diode of known thermal characteristics embedded in it. The frequency of several most important clocks can also be easily altered by reconfiguring the phase-locked loop connected to the mentioned I<sup>2</sup>C bus. To increase the design stability this circuit can be physically disconnected from the communication channel by means of hot-plug buffer. The AVR microcontroller is also responsible for basic interaction with the user: it constantly reads the state of the AMC handle and provides the visual feedback using the status LEDs.

All the already mentioned components are powered from the Management Power, which becomes available just after the module insertion. The CPLD circuit is the only MMC component located in the Payload Power domain, which is enabled only after a successful card activation. All connections between those domains are carefully separated with suitable buffers, to avoid unwanted power leakage to the disabled circuity. The programmable logic device is used as a twoport I/O expander with dedicated controllers for several more complex peripherals. It has serial interfaces both to the microcontroller and to the payload circuits, enabling the configuration to be changed by IPMC commands or by the user application in the module. Through those interfaces the CPLD offers a set of registers supporting sequential and random access. Most importantly, the registers provide control over the payload FPGA configuration process, gating of the clocks and multiplexing of the high-speed serial lanes. They also enable modifications of the built-in JTAG chain to accommodate for various configuration or protection requirements.

## B. MMC firmware

As it was mentioned, the ATMEGA 1281 controller fulfills the most important role in the Module Management

Fig. 3. Structure of Module Management Controller

Controller of the  $\mu$ TUC board. It is the heart of the MMC, because it implements functionalities required by the MTCA.4 specification and is responsible for control of other devices comprising the MMC.

The firmware described in this paper was prepared mainly for the needs of tests and debugging and it is not a final version that will be used on the  $\mu TC$  board. However, even though the firmware was prepared for test purposes it implements functionalities described in MTCA.4 specification, especially in the range of  $\mu RTM$  handling. Unfortunately, the MTCA.4 is still under development. Consequently, other devices, especially MCH modules, fully compatible with this specification are not yet available on the market. Thus, development of software for the MMC is difficult due to the lack of possibilities of testing and debugging.

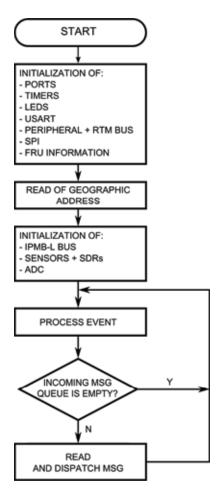

The schematic of firmware which provides necessary MMC functionalities is presented in Figure 4. As one can see, the algorithm can be divided into two basic parts: the initialization part and the main loop. The initialization part is performed only once, immediately after the microcontroller reset. Its task is to prepare software structures and peripheral devices be used by MMC during operation. At the beginning of the initialization part the microcontroller I/O ports as well as built-in timers are configured. The task of the timers is generation of events in definite time intervals e.g. every 1 ms or 10 ms which allows to perform some functions in a cyclic way. These functions are responsible for LED control, monitoring of Hot Swap handle state and RTM presence signal, reading

data from sensor and the like. In the next step the structures for LED control are initialized. They store information about actual state and settings of LEDs controlled by the MMC. Then, the USART interface for debug purposes and two I<sup>2</sup>C buses for communication with on-board devices and  $\mu$ RTM are initialized. It should be noted that the peripheral and μRTM I<sup>2</sup>C buses were implemented as software I<sup>2</sup>C buses, because the used microcontroller is equipped with only one built-in I<sup>2</sup>C interface connected to the IPMB-L bus. After that, the SPI interface is configured. It is connected to the CPLD and gives the possibility to control on-board signals by reading/writing appropriate registers. Next, the structure storing FRU Information is initialized. The data from this structure are read by the Carrier Manager during module activation. They provide information about the board as a whole, power supply requirements and interfaces available on the board.

The next step is to read and decode the Geographic Address that is used to uniquely identify the module in the  $\mu$ TCA Carrier. This address is provided by the carrier using three pins which can be connected to ground, to Management Power or left unconnected. Each combination of states of Geographic Address pins has assigned corresponding I<sup>2</sup>C address which shall be used as the slave address of the MMC in communication with the Carrier Manager. After obtaining the Geographic Address, the configuration of the built-in I<sup>2</sup>C controller is possible. As it was mentioned, this interface is connected to the IPMB-L bus and for this reason its slave

address has to be initialized with the Geographic Address. The module's slave address is also used in SDR structures. Therefore, in the next step they are filled in an appropriate way. The initialization part ends with the configuration of the analog-to-digital converter. The ADC is used to measure the 12 V voltage. On this basis the MMC detects whether the Payload Power is turned on or not.

The firmware for microcontroller was written based on the principles of event-driven programming [14]. It means that the flow of the program is determined by events. The events are triggered mainly in interrupt service routines, but their handling takes place in the main loop. For this reason the first step in the main loop is event processing. The information about events is stored in one 16-bit variable. Each event has a corresponding bit in this variable which is set when the event occurs. In the function responsible for events processing all the flags are checked and appropriate actions are taken. The current version of the firmware implements events informing that the Hot Swap handle was opened/closed, Payload Power was turned on/off or  $\mu$ RTM was connected/disconnected. There are also events generated by timers in defined time intervals. The event indicating that  $\mu$ RTM was connected is a starting point for the  $\mu$ RTM activation. After detection of the  $\mu RTM$  presence the MMC turns on the Blue Led on the it and verifies the compatibility. Then the MMC begins

Fig. 4. Algorithm of MMC firmware

continuous monitoring of the  $\mu$ RTM Hot Swap handle state. When the Hot Swap handle is closed, the MMC should send appropriate event message to the Carrier Manager. However, due to the fact, that fully compatible MCH modules are currently not available, testing of further steps of activation is still in progress.

After event processing the MMC handles messages received from the Carrier Manager via the IPMB-L bus. Firstly, the message is decoded and then required actions are taken and response for the Carrier Manager is prepared. In order to increase the communication reliability all incoming messages are stored in a FIFO queue from which they are read in the handling procedure. A similar queue is also implemented for outgoing messages, but only requests from the MMC to the Carrier Manager to this queue are added. Responses are sent directly to the Carrier Manager. Thanks to the application of the outgoing queue, requests can be repeated if need be. These two steps: event processing and message handling are performed in an infinite loop.

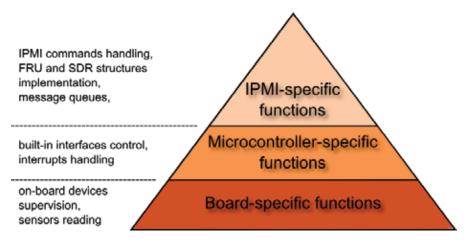

The software for the microcontroller was written in such a way that it is possible to distinguish three fundamental parts presented in Figure 5. The first one includes functions which provide functionalities required by the MicroTCA standard e.g. message handling, SDR and FRU structures and message queues. These functions should be independent of the platform. In the second part are functions specific for microcontroller e.g. I/O ports configuration, interrupts handling or communication interfaces configuration. The last one part includes functions dependent on the board on which the software will be used. These functions may be responsible for sensors reading or configuration of on-board devices. This division of software code is aimed at software portability. The software can be applied for another boards and only the change of the lowest layers is necessary. The highest layer of this structure is constant and may be common for many projects.

Fig. 6. Laboratory test stand

Fig. 5. Structure of firmware code

Described software was tested in laboratory test stand presented in Figure 6. System for test purposes was built on the base of xTCA platform fabricated by the ELMA company. This platform is compliant with MicroTCA.4 specification. It provides 6 slots for AMC Double Modules and one slot for the MCH module. It also includes the Power Module and the Cooling Unit. The MCH module used during the tests is the NAT-MCH Gen3 [15]. It implements functionalities both the Carrier Manager and the Shelf Manager and it can manage up to 12 AMC modules, 2 cooling units and 4 power modules. Furthermore, it is also equipped with clock distribution module and PCI Express switch. During the tests in the shelf are also present additional modules e.g. AMC Processor Module — AMC-1000 [16] and SATA Drive Module — SB-AMC45 [17]. The developed firmware worked properly during the tests. The microcontroller under its control provides functionalities required for the MMC. It communicates with the Carrier Manager correctly and makes the FRU and SDR information available. The MMC activates and deactivates the module properly. The time of activation process equals about 3-5 s for first activation after module insertion and 500-1000 ms in case of module reactivation. The difference is caused by the fact, that Carrier Manager collects information about the module during the first activation process after insertion of the module into the shelf. When the module is deactivated and activated again these information are not collected and the activation process takes less time. In case of the deactivation, the time of whole process takes 1-2 s. Time of activation as well as deactivation is independent of number of modules in the shelf. The MMC implements also commands for sensors handling. The correctness of their operation was verified using a free version of NATview application [18] dedicated for cooperation with NAT-MCH module. This application is visualization tool for the MicroTCA system. It collects information about modules placed in the system and presents them in graphical user-friendly way. The application allows to read current value of sensors and also gives the possibility to manipulate their thresholds. The sensors available on the  $\mu$ TC board were presented correctly in NATview application what means that they were described properly using SDR

structures and the IPMI commands for their handling were implemented correctly. The MMC can also detect the presence of  $\mu$ RTM module and allows to control its supply voltages and communicate with devices connected to I<sup>2</sup>C bus. However, due to the fact that the MCH used during the tests is not fully compatible with MTCA.4 specification, it does not support  $\mu$ RTM handling. For this reason testing of functionalities involved with  $\mu$ RTM activation and deactivation was not possible.

# IV. SUMMARY

The MTCA.4 specification brings considerable changes in the management layer of the  $\mu$ TCA standard. They are mainly involved with supervising of the  $\mu$ RTM module which was introduced by this specification. In MicroTCA for Physics systems the MMC of AMC board is responsible for control and management of the  $\mu$ RTM. Due to the fact that the  $\mu$ RTM is not an intelligent module, the MMC is also responsible for its representation in communication with the Carrier Manager. The MMC described in this paper is one of the first solutions designed for the AMC module compatible with the MTCA.4 specification. It provides fundamental functionalities allowing the  $\mu RTM$  handling. Unfortunately, the testing and debugging of this MMC was difficult, because this new specification is still under development and compatible devices, mainly MCH modules, are no yet available on the market. However, although the presented version of the firmware for the MMC is not a final version, it may be a good basis for further development of management controllers for MTCA.4-compliant modules.

### ACKNOWLEDGMENTS

The research leading to these results has received funding from the European Commission under the EuCARD FP7 Research Infrastructures grant agreement no. 227579. The authors are scholarship holders of project entitled "Innovative education ..." supported by European Social Fund.

#### REFERENCES

- [1] "PICMG MTCA.0 Micro Telecommunications Computing Architecture Base Specification."

- [2] "PICMG 3.0 AdvancedTCA® Base Specification."

- [3] "PICMG AMC.0 Advanced Mezzanine Card Base Specification."

- [4] C. Foudas, J. Jones, and M. Stettler, "DAQ and Control Systems for the CMS Global Calorimeter Trigger Matrix Processor," *IEEE Nuclear Science Symposium*, 2008.

- [5] R. Cerne, Z. Lestan, U. Mavric, B. Repic, B. Baricevic, A. Bardorfer, P. Beltram, T. Beltram, J. Menart, G. Jug, and C. Bocchetta, "Digital RF Stabilization System Based on MicroTCA Technology," 17th IEEE-NPSS Real Time Conference, 2010.

- [6] M. Drochner, P. Kämmerling, H. Kleines, and P. Wüstner, "MicroTCA Developments for PANDA Data Acquisition," 17th IEEE-NPSS Real Time Conference, 2010.

- [7] A. B. Mann, I. Konorov, H. Angerer, Markus Krämer, S. Huber, B. Grube, J. Friedrich, B. Ketzer, S. Uhl, F. Haas, A.-M. Dinkelbach, S. Grabmüller, and S. Paul, "The Universal Sampling ADC Readout System of the COMPASS Experiment," *IEEE Nuclear Science Symposium*, 2009.

- [8] R. S. Larsen, "PICMG xTCA Standards Extensions for Physics: New Developments and Future Plans," 17th IEEE-NPSS Real Time Conference, 2010.

- [9] D. Makowski, W. Koprek, T. Jeżyński, A. Piotrowski, G. Jabłoński, W. Jałmużna, and S. Simrock, "Interfaces and Communication Protocols in ATCA-Based LLRF Control Systems," *IEEE Transactions on Nuclear Science*, vol. 56, no. 5, pp. 2814–2820, October 2009.

- [10] U. Mavric, B. Chase, and M. Vidmar, "Design and evaluation of a low-level RF control system analog/digital receiver for the ILC main LINACs," *Nuclear Instruments and Methods in Physics Research A*, vol. 594, no. 1, pp. 90–96, August 2008.

- [11] GE Fanuc Embedded Systems, "MicroTCA System Management." [Online]. Available: http://www.acaltechnology.com/\_files/franchise/GE\_Fanuc/whitepapers/uTCA%20sys%20management.pdf

- [12] "Intelligent Platform Management Interface Specification Second Generation v2.0."

- [13] D. Makowski, G. Jabłoński, A. Mielczarek, A.Napieralski, P. Perek, P. Prędki, T. Jeżyński, F. Ludwig, and H. Schlarb, "uTCA-based Controller," MIXDES 2011, 16-18 June 2011.

- [14] P. A. Laplante, Real-Time System Design and Analysis. Wiley, 2004, pp. 74-76.

- [15] [Online]. Available: http://www.nateurope.com/products/amc/nat-mch.htm

- [16] [Online]. Available: http://www.adlinktech.com/PD/web/PD\_detail.php?cKind=&pid=729&seq=&id=&sid=

- [17] [Online]. Available: http://www.sanblaze.com/support/embeddedproducts/amc/amc-storage-modules-amc3/sb-amc45

- [18] [Online]. Available: http://www.nateurope.com/products/amc/natView.htm

Andrzej Napieralski received the M.Sc. and Ph.D. degrees from the Technical University of Łódź (TUL) in 1973 and 1977, respectively, and a D.Sc. degree in electronics from the Warsaw University of Technology (Poland) and in microelectronics from the Université de Paul Sabatié (France) in 1989. Since 1996 he has been a Director of the Department of Microelectronics and Computer Science. Between 2002 and 2008 he held a position of the Vice-President of TUL. He is an author or co-author of over 900 publications and editor of 18 conference

proceedings and 12 scientific Journals. He supervised 44 PhD theses; five of them received the price of the Prime Minister of Poland. In 2008 he received the Degree of Honorary Doctor of Yaroslaw the Wise Novgorod State University (Russia).

**Piotr Perek** received the MSc degree in the field of Electronics and Telecommunications at the Technical University of Lodz in 2010. He continues his education as a PhD student at the Department of Microelectronics and Computer Science TUL. His interests include embedded systems, programmable devices and software development. His recent research concerns the development of control and data acquisition systems based on ATCA,  $\mu$ TCA and AMC standards.

Aleksander Mielczarek received M.Sc. degree in electrical engineering at the Department of Microelectronics and Computer Science Technical University of Lodz in 2010. His main areas of interests are embedded systems, integrated sensors and high speed communication links. He is involved in the development of control and data acquisition systems for Free-electron LASer in Hamburg (FLASH), a project carried by Deutsches Elektronen-Synchrotron (DESY).

Paweł Prędki graduated from the International Faculty of Engineering at the Techical University of Łódź in 2009 with an MSc degree in Telecommunications and Computer Science. He continues his education as a PhD student at TUL and is involved in many projects. His main fields of interest are embedded systems and digital signal processing. He also deals with control systems and data acquisition systems based on the ATCA and  $\mu$ TCA architectures.

Dariusz Makowski received Ph.D. degree in electrical engineering at the Department of Microelectronics and Computer Science Technical University of Łódź in 2006. His main areas of interests are digital electronics, embedded systems and programmable devices. He is involved in the development of xTCA standards for High Energy Physics. He is engaged in the design of distributed data acquisition and control systems based on ATCA, μTCA and AMC standards.